Verdú, Multiuser Detection, Cambridge University Press, Cambridge, 1998. Moshavi, “Multi-User Detection for DS-CDMA Communications,” IEEE Communications Magazine, Oct. Proakis, Digital Communications, New York: McGraw-Hill, 1989. The detector, handling up to eight users with 12-bit fixed point precision, was fabricated using a 1.2 μm CMOS technology and can process 190 Kbps/user for 8 users. A VLSI implementation of the differencing multistage detector is built to demonstrate the computational savings and the real-time performance potential. By using just two stages of the differencing detector, we achieve predictable execution time with performance equivalent to at least eight stages of the regular multistage detector. However, the convergence of the algorithm is dependent on the number of users, the interference and the signal to noise ratio and hence, the detection has a variable execution time. Multiplication by ☒ can be easily implemented in hardware as arithmetic shifts.

Bypassing the zero terms saves computations. Under the assumption of BPSK modulation, the differences between the bit estimates from consecutive stages are 0 and ☒.

When interference cancellation converges, the difference of the detection vectors between two consecutive stages is mostly zero. In this paper, we propose a real-time VLSI implementation of this detection algorithm in the uplink system, where we have achieved both high performance in interference cancellation and computational efficiency.

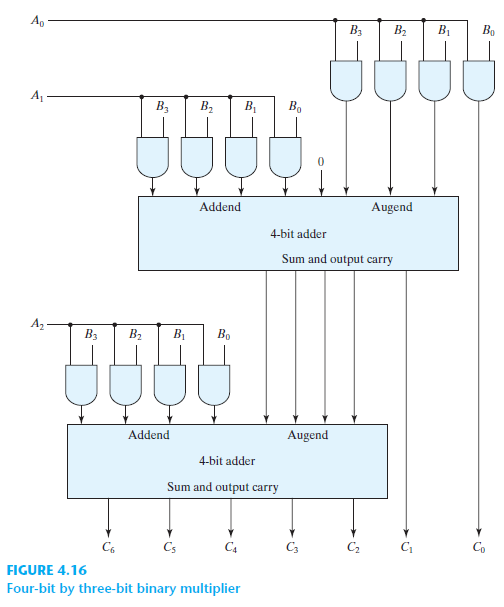

#4 bit multiplier using bit slicer code#

The multistage detection algorithm has been proposed as an effective interference cancellation scheme for next generation Wideband Code Division Multiple Access (W-CDMA) base stations.

0 kommentar(er)

0 kommentar(er)